#### 4. Síntesis de un circuito secuencial síncrono

El estudio del procedimiento de diseño de circuitos secuenciales síncronos se realiza mediante la aplicación a un sencillo ejemplo. Los puntos a desarrollar son:

- Lectura del problema y definición de variables.

- Construcción del diagrama tabla y de estados.

- Minimización de estados y obtención de la tabla equivalente que contenga el número mínimo de estados.

- Determinación del numero de FFs necesarios y completar los mapas de excitación de los FF seleccionados.

- Asignación de estados y generación de tablas de transición de estados y salidas.

- Obtención de las ecuaciones para los circuitos combinacionales.Implementación del circuito secuencial.

Todos los pasos son completamente automatizables ya que son algoritmos exactos excepto el segundo que requiere cierta intuición por parte del diseñador lógico. Así pues, se debe invertir especial esfuerzo en la comprensión del problema para que resulte más sencilla la realización del diagrama de estados correspondiente.

#### 4.1. Lectura del problema y definición de variables

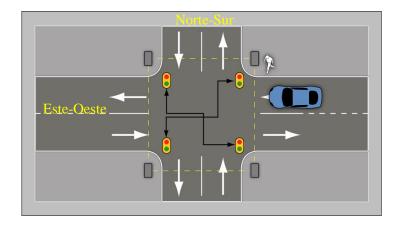

En el ejemplo propuesto se trata de diseñar una Unidad de Control para los semáforos que controlan un cruce de carreteras para vehículos. La Unidad de Control deberá tener en cuenta si hay peatones que deseen cruzar.

Las condiciones de funcionamiento son las siguientes: en caso de no haber solicitud de paso por parte de ningún peatón, circularán alternativamente durante un minuto los coches de ambas direcciones, es decir, un minuto tendrán el semáforo en verde los coches que circulen en la dirección Norte-Sur (NS) y transcurrido ese minuto su semáforo se pondrá en rojo para dar paso a los vehículos que se encuentran en la dirección Este-Oeste (EO) durante otro minuto. En esta situación de alternancia se mantendrán hasta que haya solicitud de paso por parte de algún peatón. En ese caso, transcurrido el minuto de paso que le corresponde a los coches que estuvieran circulando, se pondrán todos los semáforos en rojo durante un minuto y permitir así que el peatón cruce por cualquiera de las dos calles.

Electrónica Digital. - 262 -

No hay peatones

1 min NS

1 min. EO

Hay peatones

1 min.

NS rojo

EO rojo

Una vez comprendido el funcionamiento del circuito o sistema a diseñar, se deben definir las variables de entrada y de salida.

En este caso la única entrada a definir será la solicitud de paso por parte de algún peatón que denominamos *P*. Esta variable tomará el valor 1 en caso de haber solicitud.

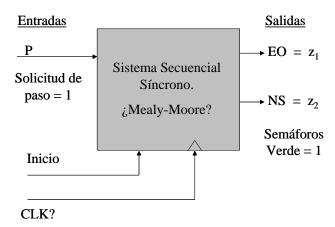

Las salidas serán las variables que determinen el estado de los semáforos: rojo o verde. Puesto que los semáforos a controlar son dos, se definen dos variables de salida, una para la calle EO  $(z_1)$  y otra para la calle NS  $(z_2)$ . El estado verde se representa con el valor 1.

Ta y como se ha expuesto en el Diagrama General de los S.S.S., se dispone de una entrada de Inicio y de Reloj (CLK). El periodo de éste será de un minuto.

Tanto las entradas como las salidas se han recuido en la Figura 193. Ahí también se plantea otro aspecto a deducir antes de proseguir con el diseño, esto es, la elección de modelo (*Mealy* o *Moore*).

Figura 193

Teniendo en cuenta la descripción del sistema, debe elegirse el modelo *Moore* ya que se desea que a pesar de haber petición de paso por parte de algún peatón, el estado de los semáforos se mantenga hasta la conclusión del minuto.

Electrónica Digital. - 263 -

Resumiendo, el sistema deberá disponer de una entrada P que indique solicitud de paso de un peatón, una entrada de Reloj CLK con un periodo de un minuto y una entrada de *Inicio* que permita llevar al sistema a un estado predeterminado. Por otro lado, las salidas serán dos,  $z_1$  para controlar el semáforo de la calle EO y  $z_2$  para controlar el semáforo de la calle NS. Aplicando estas variables al Diagrama General S.S.S. obtenemos la Figura 194.

Figura 194.

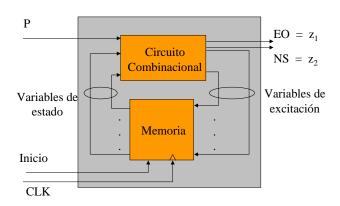

Puesto que el modelo debe ser Moore y las salidas única y exclusivamente dependen del estado del sistema se puede redistribuir el Diagrama General como se muestra en la Figura 195.

Figura 195.

### 4.2. Construcción del Diagrama y de Tabla de estados.

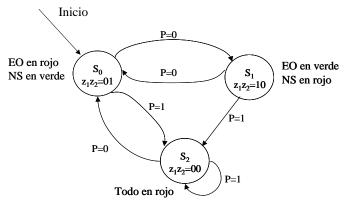

Los estados en los que se puede encontrar este sistema, a priori, se puede decir que son tres: Verde el semáforo para los coches que circulan en la dirección NS, verde el semáforo para los coches que circulan en la dirección EO y todos los semáforos en rojo. A partir de estos estados se pueden representar las transiciones según la Figura 196.

Electrónica Digital. - 264 -

Figura 196

Sin embargo con un análisis superficial de ese diseño, se puede observar que presenta dos deficiencias:

La primera, estando en el estado  $S_2$  si uno o varios peatones continuamente solicitan paso, se bloquearía el trafico por un tiempo indefinido.

La segunda, podría ocurrir que el sistema se quede alternando entre los estados  $S_0$  y  $S_2$  bloqueando el trafico en la dirección EO.

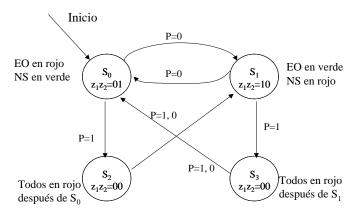

La solución al segundo problema viene dada por la inclusión en el diagrama de estados de estados que recuerden qué dirección fue la última en tener el semáforo en verde. El primer problema se soluciona simplemente realizando una adecuada asignación a las transiciones de estado. Así pues, la solución correcta sería la expresada en la Figura 197.

Figura 197.

A partir del diagrama de estados la tabla de estados se obtiene sin problema alguno (Tabla 40).

Electrónica Digital. - 265 -

|                  |       | Entrada P |       | Sali  | das   |

|------------------|-------|-----------|-------|-------|-------|

|                  |       | 0   1     |       | $Z_1$ | $Z_2$ |

| Estado<br>actual | $S_0$ | $S_1$     | $S_2$ | 0     | 1     |

|                  | $S_1$ | $S_0$     | $S_3$ | 1     | 0     |

|                  | $S_2$ | $S_1$     | $S_1$ | 0     | 0     |

|                  | $S_3$ | $S_0$     | $S_0$ | 0     | 0     |

|                  |       |           |       |       |       |

Estado siguiente

Tabla 40

#### 4.3. Minimización de estados

Una vez completada la tabla de estados es importante detenerse a inspeccionarla por si hubiese algún estado simplificable, es decir, diferentes estados de la tabla que efectúen la misma función y por lo tanto no se puedan distinguir por medio de las mediciones de salida. En caso de haberlos, se sustituirían por uno de ellos únicamente.

En el sistema bajo estudio, los únicos estados que podrían ser simplificables son  $S_2$  y  $S_3$  ya que  $S_1$  y  $S_2$  proporcionan salidas distintas. Sin embargo, continuando con el estudio de  $S_2$  y  $S_3$ , inmediatamente se hace evidente la diferencia entre ambos ante cualquier valor de la entrada P, ya que la evolución al siguiente estado provoca salidas distintas en ambos y por lo tanto, no se puede decir que sean indistinguibles estos dos estados.

Concluyendo, la tabla obtenida no presenta ningún estado simplificable.

#### 4.4. Determinación del numero de FFs necesarios. Mapas de excitación.

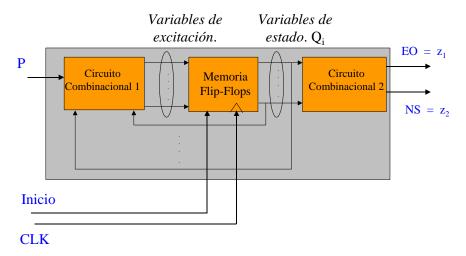

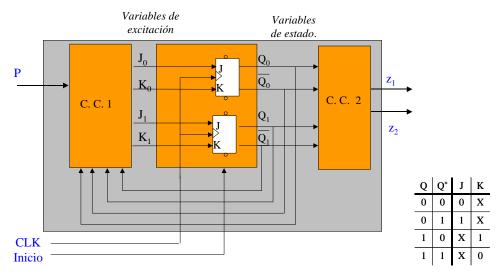

Una vez determinados el número de estados que debe contener el sistema a diseñar, sabemos que que cada estado deberá representarse mediante una combinación de las Variables de Estado. Puesto que tenemos cuatro estados (S<sub>0</sub>, S<sub>1</sub>, S<sub>2</sub>, S<sub>3</sub>) el número de variables de estado será dos (Q<sub>1</sub> Q<sub>0</sub>) y por lo tanto dos *flip-flops* (FF<sub>1</sub>, FF<sub>0</sub>). Se realizará el diseño a partir de *flip-flops* JK. Aplicando estos elementos de memoria al Diagrama General del S.S.S. obtenemos la Figura 198. En ella se ha representado igualmente la tabla de excitación de un FF JK.

Electrónica Digital. - 266 -

Figura 198.

# 4.5. Asignación de estados y generación de tablas de transición de estados y salidas

El siguiente paso será asignar a cada estado  $(S_0, S_1, S_2, S_3)$  una combinación determinada de las variables de estado  $(Q_1 Q_0)$ . Una opción sería la representada en la Tabla 41.

|          |                | Entrada P |       | Sali  | idas  |

|----------|----------------|-----------|-------|-------|-------|

| $Q_1Q_0$ |                | 0         | 1     | $Z_1$ | $Z_2$ |

| 00       | $S_0$          | $S_1$     | $S_2$ | 0     | 1     |

| 01       | $S_1$          | $S_0$     | $S_3$ | 1     | 0     |

| 10       | $S_2$          | $S_1$     | $S_1$ | 0     | 0     |

| 11       | S <sub>3</sub> | $S_0$     | So    | 0     | 0     |

Tabla 41.

Sustituyendo en la tabla los valores asignados a las variables de estado, se obtiene la Tabla 42.

|          |       | Entrada P |    | Salio | das   |

|----------|-------|-----------|----|-------|-------|

| $Q_1Q_0$ |       | 0         | 1  | $Z_1$ | $Z_2$ |

| 00       | $S_0$ | 01        | 10 | 0     | 1     |

| 01       | $S_1$ | 00        | 11 | 1     | 0     |

| 10       | $S_2$ | 01        | 01 | 0     | 0     |

| 11       | $S_3$ | 00        | 00 | 0     | 0     |

Tabla 42

La información que proporciona esta tabla permitirá generar la Tablas de Transición de Estados, es decir tablas en la que aparezcan los valores que deben tomar las variables de excitación de los flip-flops para conseguir que se cumplan las transiciones descritas en la tabla. Suponiendo que el sistema se encuentre en el estado  $S_0$  el valor de las variables

Electrónica Digital. - 267 -

de estado será  $Q_1Q_0 = 00$ . Tras una entrada de P = 1 el sistema evoluciona al estado  $S_2$  con  $Q_1Q_0 = 10$ . Se observa que la variable de estado  $Q_1$  realiza una transición de 0 a 1 mientras que la variable  $Q_0$  se mantiene a 0. Para que esto ocurra es necesario que las variables de excitación tomen unos valores concretos. Ba´sándonos en la tabla de excitación de lo FF JK (Tabla 43) se concluye que esos valores serán  $J_1K_1 = 1X$  y  $J_0K_0 = 0X$ . Realizando este estudio para todas las posibles transiciones se obtiene la tabla de transición representada en la Tabla 44 donde también aparecen reflejados los valores que toman las salidas en cada estado.

| Q | $Q^*$ | J | K |

|---|-------|---|---|

| 0 | 0     | 0 | X |

| 0 | 1     | 1 | X |

| 1 | 0     | X | 1 |

| 1 | 1     | X | 0 |

Tabla 43

|                  |          | P:       | =0                        | P               | =1                        |       |       |

|------------------|----------|----------|---------------------------|-----------------|---------------------------|-------|-------|

|                  | $Q_1Q_0$ | $J_1K_1$ | $\int_{0}^{\infty} K_{0}$ | $\int_{1}K_{1}$ | $\int_{0}^{\infty} K_{0}$ | $Z_1$ | $Z_2$ |

| $S_0$            | 0 0      | 0 X      | 1 X                       | 1 X             | 0 X                       | 0     | 1     |

| $\overline{S_1}$ | 0 1      | 0 X      | X 1                       | 1 X             | X 0                       | 1     | 0     |

| $\overline{S_2}$ | 10       | X 1      | 1 X                       | X 1             | 1 X                       | 0     | 0     |

| $\overline{S_3}$ | 1 1      | X 1      | X 1                       | X 1             | X 1                       | 0     | 0     |

Tabla 44.

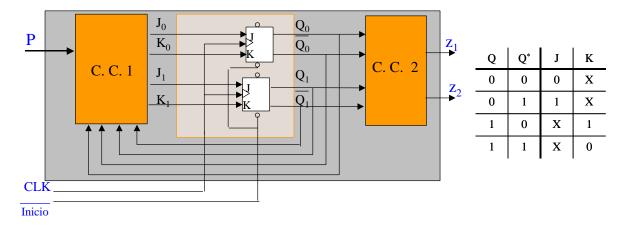

Otro dato que obtenemos a partir de la Tabla 44. es la definición de la entrada de *Inicio*. En el diagrama, a este estado se le ha asignado el estado  $S_0$  y según la Tabla 44. el valor de su estado será  $Q_1Q_0=00$ . Este estado se consigue simplemente cableando la entrada *Inicio* a las entradas asíncronas de reseteo de los FF tal y como se ha hecho en la Figura 199.

Electrónica Digital. - 268 -

Figura 199

# 4.6. Obtención de las ecuaciones combinacionales

A partir de la Tabla 44 se pueden obtener las Tablas de Verdad de los circuitos combinacionales del Diagrama General del sistema a diseñar. Si se observa este diagrama se concluye rápidamente que el denominado Circuito Combinacional 1 presenta como entradas  $Q_1$ ,  $Q_0$  y P y como salidas  $J_1K_1$ ,  $J_0K_0$  y en el Circuito Combinacional 2 las entradas son  $Q_1Q_0$  y las salidas  $Z_1$  y  $Z_2$ . Las relaciones entre estas entradas y salidas aparecen en la Tabla 44 por lo que se pueden extraer la Tablas de Verdad para el Combinacional 1 (Tabla 45. (a)) y para el Combinacional 2 (Tabla 45. (b)).

|                  | $PQ_1Q_0$ | $J_1K_1$ | $J_0K_0$ |   |                  |          |       |       |

|------------------|-----------|----------|----------|---|------------------|----------|-------|-------|

| $S_0$            | 000       | 0 X      | 1 X      |   |                  |          |       |       |

| $S_1$            | 001       | 0 X      | X 1      |   |                  |          |       |       |

| $S_2$            | 010       | X 1      | 1 X      | _ |                  | $Q_1Q_0$ | $Z_1$ | $Z_2$ |

| $S_3$            | 011       | X 1      | X 1      | _ | $\overline{S_0}$ | 00       | 0     | 1     |

| $S_0$            | 100       | 1 X      | 0 X      |   |                  |          |       |       |

| $\overline{S_1}$ | 101       | 1 X      | X 0      | - | $S_1$            | 0 1      | 1     | 0     |

| $\overline{S_2}$ | 110       | X 1      | 1 X      | - | $S_2$            | 10       | 0     | 0     |

| $\overline{S_3}$ | 111       | X 1      | X 1      | - | $S_3$            | 11       | 0     | 0     |

|                  | (a)       | )        |          |   |                  |          | (b)   |       |

Tabla 45.

Un vez realizada la simplificación lógica de las salidas utilizando los Mapas de Karnaugh se obtienen las siguientes funciones lógicas:

Electrónica Digital. - 269 -

$$Z_{2} = \overline{Q}_{1} + \overline{Q}_{0}$$

$$Z_{1} = \overline{Q}_{1} + Q_{0}$$

$$J_{1} = P$$

$$K_{1} = 1$$

$$J_{0} = K_{0} = \overline{P} + Q_{1}$$

Cabe destacar en este punto la dependencia de estas funciones con la asignación de estados realizada, ya que a partir de esta asignación la Tabla de Transición será distinta para distintas asignaciones de estados y por lo tanto, las Tablas de Verdad de los circuitos combinacionales, y consecuentemente la funciones lógicas fínales, también. Veamos un ejemplo de ese hecho. Supongamos que se ha realizado la asignación de estados representada en la Tabla 46.

|          |                | Entr           | ada P          | Salidas |       |

|----------|----------------|----------------|----------------|---------|-------|

| $Q_1Q_0$ |                | 0              | 1              | $Z_1$   | $Z_2$ |

| 00       | $S_0$          | $S_1$          | $S_2$          | 0       | 1     |

| 10       | $S_1$          | $S_0$          | $S_3$          | 1       | 0     |

| 11       | $S_2$          | $S_1$          | S <sub>1</sub> | 0       | 0     |

| 01       | S <sub>3</sub> | S <sub>0</sub> | S <sub>0</sub> | 0       | 0     |

Tabla 46

En ese caso, la ecuacione slogicas que se obtienen sigueindo el procedimiento explicado serían las siguientes:

$$Z_{2} = Q_{1} + \overline{Q}_{0}$$

$$Z_{1} = \overline{Q}_{1} + \overline{Q}_{0}$$

$$J_{1} = K_{1} = \overline{Q}_{0}$$

$$J_{0} = P$$

$$K_{0} = 1$$

# 4.7. Implementación del circuito secuencial

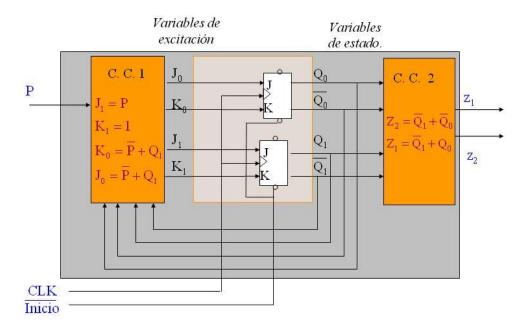

A partir de las funciones lógicas relativas a los circuitos combinacionales se completa el Diagrama General para el diseño de la Unidad de control como se muestra en la Figura 200.

Electrónica Digital. - 270 -

Figura 200.

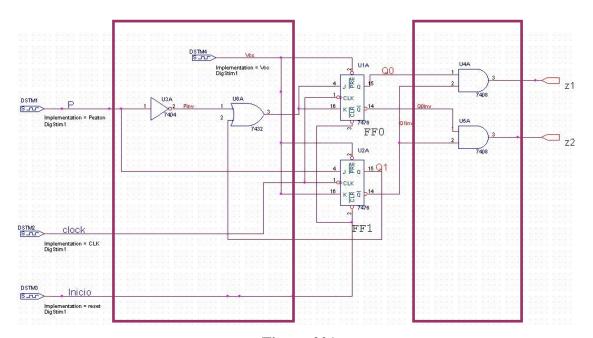

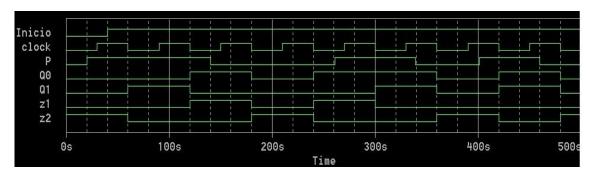

El último paso para la conclusión será simular este circuito mediante algún programa de CAD para el diseño de circuitos digitales como puede ser el OrCAD Capture 9.0. Para el diseño se ha elegido el *flip-flop* JK 7476 con entradas asíncronas de carga y reseteo, y con activación de flanco de reloj descendente. El circuito lógico se presenta en la Figura 201. donde la variable *clear* se corresponde con la de *Inicio*. En la Figura 202 se puede analizar la respuesta del circuito y comprobar así su correcto funcionamiento.

Figura 201.

Electrónica Digital. - 271 -

Figura 202

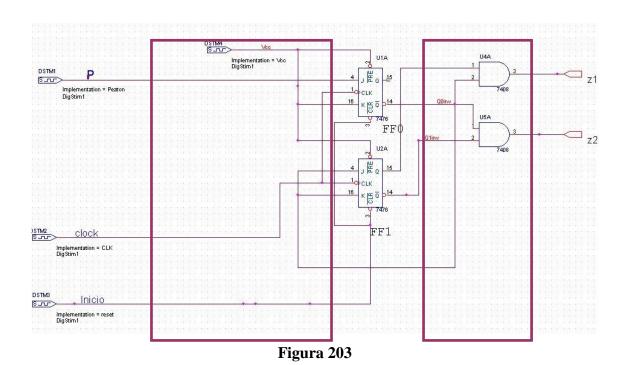

Si se realiza la implementación del circuito secuencial utilizando la asignación de estados alternativa propuesta en la Tabla 46, el circuito lógico correpondiente es el representado en la Figura 203 y la simulación en la Figura 204.

Figura 204

Electrónica Digital. - 272 -