## 8. Multiplexores Digitales

El multiplexor permite seleccinar del total de líneas de entrada una única y trasladar la información que conlleva dicha línea a la salida del circuito. Suele utilizarse para convertir información digital en paralelo a serie.

## 8.1. Diseño

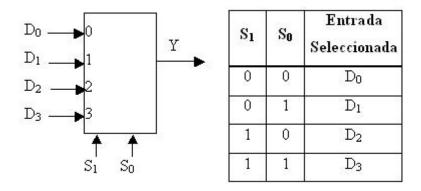

El diseño para un multiplexor con cuatro entradas a seleccionar, requerirá dos variables de entrada que permitan dicha selección, ya que con dos bits se logran cuatro combinaciones. El esquema del circuito y su tabla de funcionamiento se muestra en la Figura 117.

Figura 117

A partir de la tabla y de la descripción verbal se obtiene la siguiente función lógica:

$$Y = D_0 \overline{S_1} \overline{S_0} + D_1 \overline{S_1} S_0 + D_2 S_1 \overline{S_0} + D_3 S_1 S_0$$

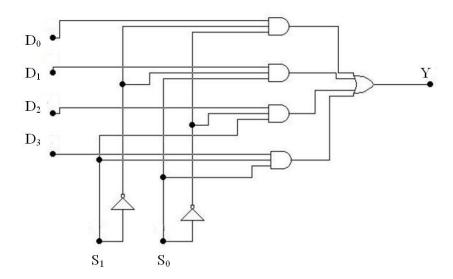

El diagrama lógico correspondiente se muesta el la Figura 118.

Figura 118

## 8.2. Implementación de funciones con multiplexores

Los MSI multiplexores puden utilizarse para generar funciones lógicas combinacionales en forma de suma de productos y así, reducir el número de circuitos integrados. Para ello, se utiliza la expresión genérica de la salida de cualquier multiplexor y se asignan valores necesarios a las entradas para obtener la función canónica deseada expresada en SDP. Veamos un ejemplo. Supongamos que disponemos de un mux con tres entradas de selección. La función genérica que representa la salida de este tipo de multiplexor será:

$$Y = D_0 \overline{S}_2 \overline{S_1} \overline{S_0} + D_1 \overline{S}_2 \overline{S_1} S_0 + D_2 \overline{S}_2 S_1 \overline{S_0} + D_3 \overline{S}_2 S_1 S_0 + D_4 S_2 \overline{S_1} \overline{S_0} + D_5 S_2 \overline{S_1} S_0 + D_6 S_2 S_1 \overline{S_0} + D_7 S_2 S_1 S_0$$

Si queremos generar la siguiente función:  $f = \Sigma m(0, 2, 3, 5)$  su expresión en SDP será:

$$f(X_2 X_1 X_0) = 1. \overline{X}_2 \overline{X_1} \overline{S_0} + 0. \overline{X}_2 \overline{X_1} \overline{X_0} + 1. \overline{X}_2 \overline{X_1} \overline{X_0} + 1. \overline{X}_2 \overline{X_1} \overline{X_0} + 0. \overline{X}_2 \overline$$

Comparando las dos expresines, se observa que asignando los siguientes valores a los  $D_i$  se obtiene la expresión de  $f(X_2X_1X_0)$

$$\begin{aligned} &D_0 = 1 & & D_1 = 0 & & D_2 = 1 & & D_3 = 1 \\ &D_4 = 0 & & D_5 = 1 & & D_6 = 0 & & D_7 = O \end{aligned}$$

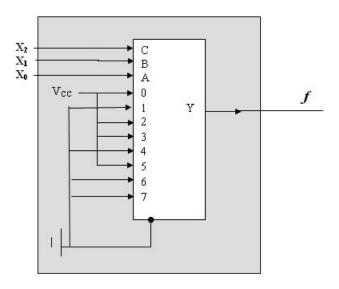

La implemtación se representa en la Figura 119:

Figura 119

Si la función a implementar tiene más variables de entrada que el multiplexor a utilizar, basta con analizar nuevamente las dos expresiones. Supongamos que se quiere implementar la función  $f(a, b, c) = ab + \overline{bc}$  utilizando un multiplexor con dos entradas de selección. La función genérica que representa la salida de este tipo de multiplexor será:

$$Y = D_0 \overline{S_1 S_0} + D_1 \overline{S_1} S_0 + D_2 S_1 \overline{S_0} + D_3 S_1 S_0$$

Si queremos generar la siguiente función  $f(a, b, c) = ab + \overline{bc}$  su expresión en SDP será:

$$F(a,b,c) = abc + ab\overline{c} + a\overline{b}c + \overline{ab}c = m_1 + m_5 + m_6 + m_7 = 0.\overline{abc} + 1.\overline{abc} + 0.\overline{abc} + 0.\overline{abc} + 1.\overline{abc} + 1.\overline{abc} + 1.\overline{abc} + 1.\overline{abc}$$

Si se identifican dos de las variables de la función con las dos entradas de selección:

$$c = S_0$$

$b = S_1$

la expresión de F será

$$F(a,b,c) = 0.\overline{aS_1S_0} + 1.\overline{aS_1}S_0 + 0.\overline{aS_1S_0} + 0.\overline{aS_1$$

Analizando y comparnado las dos expresiones, se concluye que:

Independientemente del valor de a, ante la combinación  $\overline{S_1S_0}$  la salida debe ser 0 siempre. Por lo tanto  $D_0 = 0$ .

Independientemente del valor de a, ante la combinación  $\overline{S_1}S_0$  la salida debe ser 1 siempre. Por lo tanto  $D_1 = 1$ .

Ante la combinación  $S_1\overline{S_0}$  la salida debe ser 0 cuando el valor de a es 0 y 1 cuando el valor de a es 1. Por lo tanto  $D_2 = a$ .

Ante la combinación  $S_1S_0$  la salida debe ser 0 cuando el valor de a es 0 y 1 cuando el valor de a es 1. Por lo tanto  $D_3 = a$ .

## 8.3. Circuitos Comerciales: 74157, 74151

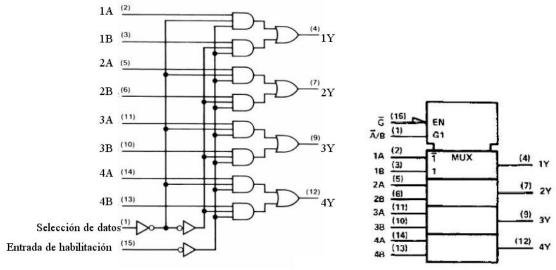

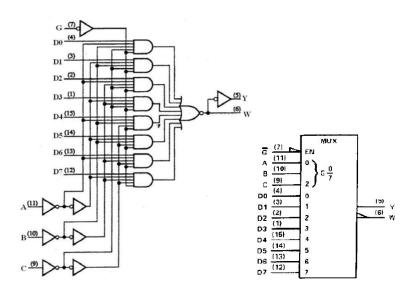

El circuito MSI 74157 está formado por cuatro multiplexores de dos entradas. Comparten la misma línea de selección de datos y de habilitación tal y como puede observarse en la Figura 120.

Figura 120

El MSI 74151 (Figura 121) es un multiplexor de ocho entradas de datos y por lo tanto tres líneas de selección de datos.

Figura 121

# 8.4. Aplicación

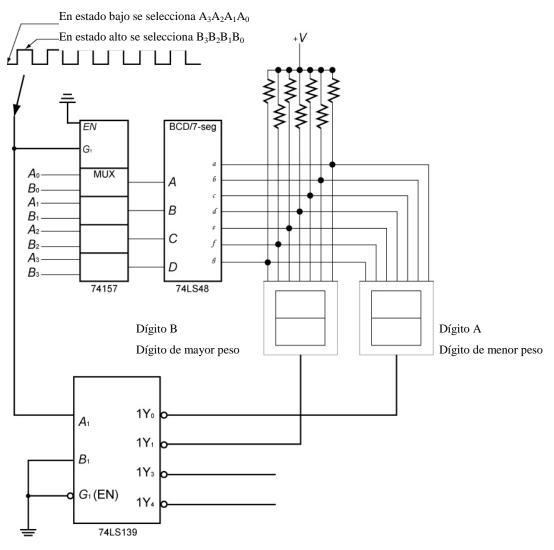

El ejemplo representado en la Figura 122 combina la utilización de un multiplexor, un decodificador 2 a 4 y un decodificador BCD/7 segmentos. Los displays van mostrando alternativamente un número, es decir, en un nivel de la señal de selección, uno de los displays está apagado y el otro muestra un número y en el otro nivel de la señal de selección, la situación es la contraria.

#### Datu-aukeratzailea

Figura 122

# 8.5. Descripción VHDL

```

entity multi is port(

1

2

a, b, c:in bit_vector(3 downto 0);

3

enable :in bit;

4

control :in bit_vector(1 downto 0);

5

d

: out bit_vector(3 downto 0)

6

);

7

end multi;

8

architecture archmul of multi is

9

begi n

10

process (a, b, c, control, enable)

11

begi n

if enable='1' then d \le "1111";

12

elsif enable='0' then

13

14

case control is

when "00" => d <= a;

15

when "01" => d \le b;

16

when "10" => d <= c;

17

18

when others => d <= "1111";

19

end case:

20

end if:

21

end process;

22

end archmul;

```